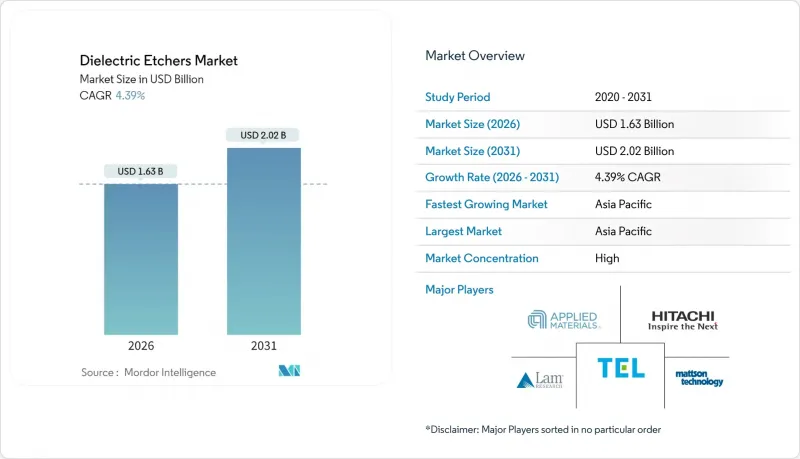

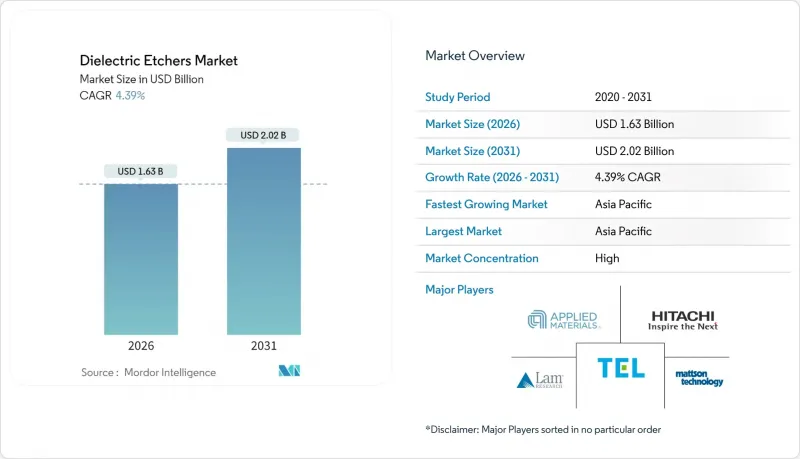

2026년 유전체 에처 시장 규모는 16억 3,000만 달러로 추정되며, 2025년 15억 6,000만 달러에서 성장하며, 2031년에는 20억 2,000만 달러에 달할 것으로 예측됩니다.

2026-2031년 연평균 복합 성장률(CAGR) 4.39%로 확대될 것으로 예측됩니다.

7nm 이하 공정에서 원자층 단위의 정밀도가 요구되고, 3D NAND의 적층 수가 증가하고, 첨단 패키징에 저유전율 유전체 채택으로 인해 디바이스 수요가 둔화되더라도 설비 투자는 높은 수준을 유지할 것입니다. 게이트 올 어라운드(GAA) 로직과 이기종 통합 기술은 장비 교체 주기를 단축하므로 파운드리는 유전체 에칭기 시장을 주도하고 있습니다. 지역별로는 아시아태평양이 설치 대수를 주도하고 있지만, 북미의 CHIPS 법에 의해 자금을 지원받은 팹과 EU의 칩스 구상이 조달 지역을 재편하고 있습니다. 다재료 공정기술과 국내 공급망을 보유한 업체는 현재 장비 업데이트의 물결을 포착하는 데 가장 유리한 위치에 있으며, 원자층 에칭(ALE), 극저온 플라즈마 모듈과 같은 정확도 향상 기술은 새로운 차별화의 길을 열어주고 있습니다.

7nm 이하 양산화는 마스크 매수를 증가시키고 공정 윈도우를 축소하므로 에칭 공정 수는 10nm 플로우에 비해 40-60% 증가합니다. GAA 트랜지스터는 고유전율 층을 손상시키지 않고 희생 SiGe를 제거해야 하며, 팹은 기존 챔버를 ALE 지원 툴로 교체해야 합니다. TSMC의 2025년 설비투자는 2nm 파일럿 라인에 중점을 두고 고선택성 유전체 모듈의 다년간의 수주를 확보하기 위해 380억-420억 달러를 투자할 예정입니다. 노드 전환이 패키징 리뉴얼과 동시에 발생하므로 장비 업데이트는 5년 주기가 아닌 3년 주기로 진행되어 유전체 에칭 시장에 안정적인 매출을 가져다 줄 수 있습니다. 고객과 화학물질을 공동 개발할 수 있는 장비 제조업체는 우선 공급자로서의 지위를 누리며 시장 진입 장벽을 강화하고 있습니다.

400층 이상의 적층 구조에 64µm 깊이의 채널홀을 에칭하기 위해서는 100:1에 가까운 종횡비 제어가 필요하며, 플라즈마의 균일성 및 부산물 배출에 부하가 걸립니다. 도쿄전자가 2025년에 도입한 극저온 에칭 기술은 휨과 뒤틀림을 줄여 램리서치의 메모리 에칭 분야에서의 우위에 대항할 수 있습니다. 32단마다의 비약적인 발전은 챔버의 재설계를 필요로 하며, 삼성을 비롯한 NAND 리더 기업은 18-24개월의 교체 주기를 요구하고 있습니다. 따라서 절연체 에칭 장비 시장은 로직 분야 수요 감소기에도 메모리 투자 수혜를 받아 매출 변동성을 완화하는 효과가 있습니다.

최첨단 절연막용 챔버는 500만-800만 달러, ALE 클러스터는 1,200만-1,500만 달러의 설치비용이 소요됩니다. 이사회 차원의 승인과 장기 임대 심사, 특히 중소형 IDM과 전문 팹의 경우, 설치가 6-12개월 지연될 수 있습니다. 업체들은 RF, 진공, 웨이퍼 핸들링 서브시스템을 공유하는 모듈식 플랫폼에 대응하여 공정 노드 간 비용을 분산시키고 있지만, 예산 제한으로 인해 단기적으로 유전체 에칭기 시장의 성장률은 여전히 70bp 감소하고 있습니다.

2025년 이산화규소는 유전체 에칭기 시장에서 38.10%의 점유율을 유지하며, 비용이 성능을 능가하는 성숙한 로직 및 DRAM 흐름을 지원했습니다. 저유전율 재료용 유전체 에칭기 시장 규모는 AI 가속기가 최소한의 용량 기판을 필요로 한다는 점을 반영하여 468.12%의 연평균 복합 성장률(CAGR)로 급성장할 것으로 예측됩니다.

저유전율 재료의 채택은 탄소 고갈 및 구리 부식을 방지하는 플라즈마 화학 처리를 필요로 하며, 기존 업체만이 대규모 상용화가 가능한 다주파 RF 기술 혁신을 촉진하고 있습니다. 동시에 질화규소 및 신흥 유리 유전체는 배리어 층 및 패널 레벨 패키징에서 틈새 역할을 수행하며 전례 없는 에칭 선택성을 요구합니다. 이러한 다양한 요구에 대응하기 위해 장비 제조업체는 현장 측정 기술 및 다중 압력 챔버를 통합해야 하며, 이는 전환 비용을 증가시켜 유전체 에칭기 시장 전체에서 매출의 다양성을 유지할 수 있습니다.

반응성 이온 에칭(RIE)은 2025년 유전체 에칭기 시장의 42.26%를 차지하며, 비용 중시 계층의 주력 기술로 자리매김할 것으로 예측됩니다. 그러나 ALEC(원자층 에칭)의 연간 5.02% 성장률은 GAA 트랜지스터, 3D NAND, 양자회로에서 그 필연성을 입증하고 있습니다.

제조업체들은 처리량 감소와 수율 향상 사이에서 고민하고 있습니다. 파일럿 데이터에 따르면 ALE가 핀 측벽의 다단계 RIE를 대체할 경우 결함 밀도가 35-45% 감소하는 것으로 나타났습니다. 도쿄일렉트론의 극저온 RIE 하이브리드 기술은 경계를 모호하게 하여 팹이 사이클 타임 예산을 지키면서 전략적으로 ALE를 도입할 수 있도록 합니다. 이러한 하이브리드화는 유전체 에칭기 시장을 세분화하여 중견 업체들이 마이크로웨이브 플라즈마나 UV 보조 공정과 같은 틈새 시장을 개발할 수 있는 여지를 만들어 주고 있습니다.

아시아태평양은 한국의 메모리 산업과 대만의 로직 산업 클러스터를 배경으로 2025년 유전체 에칭기 시장 규모의 64.51%를 차지했습니다. 중국에서만 램리서치 매출의 42%를 차지했으나, 수출규제의 역풍으로 인해 이중 소싱과 현지 장비 제조가 불가피한 상황입니다. 일본, 인도, 싱가포르 등 각국 정부의 백엔드 생태계에 대한 자금 지원으로 기존 거점을 넘어 지역적인 장비 수요가 확대되고 있습니다.

북미 CHIPS 법은 21개 주에 330억 달러 이상을 분산 투자하여 각각 500개 이상의 유전체 챔버를 필요로 하는 4개의 새로운 메가 팹 건설을 지원합니다. 국내 조달 조항으로 인해 미국 조립라인을 보유한 공급업체의 점유율이 확대되고, 단일 지역 의존에서 세계 배분 전환이 촉진되고 있습니다.

유럽은 EU 칩스법으로 주권 확보를 추진하고 있으며, 독일과 프랑스는 메모리 및 아날로그 대기업을 유치하고 있습니다. 대륙 전체 점유율은 아시아에 뒤처지지만, 주권 조달을 통한 종합적인 툴 세트(추가 기능이 아닌)에 대한 수요 증가로 성장 속도가 빨라지고 있습니다. 이러한 변화와 함께 지역 정책의 변동에 대한 수입원의 지역적 다변화로 인해 유전체 에칭기 시장은 안정화되고 있습니다.

The dielectric etchers market size in 2026 is estimated at USD 1.63 billion, growing from 2025 value of USD 1.56 billion with 2031 projections showing USD 2.02 billion, growing at 4.39% CAGR over 2026-2031.

Rising atomic-layer precision needs at sub-7 nm, escalating 3D NAND layer counts and low-k dielectric adoption in advanced packaging keep capital spending elevated even when device demand cools. Foundries continue to drive the dielectric etchers market as gate-all-around (GAA) logic and heterogeneous integration shorten equipment replacement cycles. Regionally, Asia Pacific dominates installations, but CHIPS Act-funded fabs in North America and EU Chips initiatives are reshaping procurement geography. Vendors with multi-material process know-how and domestic supply chains are best positioned to capture the current wave of re-tooling, while precision enhancements such as atomic-layer etching (ALE) and cryogenic plasma modules create new differentiation avenues.

Sub-7 nm production raises mask counts and shrinks process windows, pushing etch step totals 40-60% higher than 10 nm flows. GAA transistors require sacrificial SiGe removal without scarring high-k layers, forcing fabs to swap legacy chambers for ALE-ready tools. TSMC's USD 38-42 billion 2025 capex focuses on 2 nm pilot lines, locking in multi-year orders for high-selectivity dielectric modules. Because node migrations now coincide with packaging overhauls, tool refreshes happen on a three-year rather than five-year cadence, anchoring steady revenue for the dielectric etchers market. Equipment makers that can co-develop chemistries with customers enjoy preferred-supplier status, reinforcing market entry barriers.

Etching 64 µm-deep channel holes through above 400-layer stacks demands aspect-ratio control near 100:1, pressuring plasma uniformity and by-product evacuation. Cryogenic etch launched by Tokyo Electron in 2025 mitigates bowing and twisting, answering Lam Research's hold in memory etch. Each 32-layer leap forces chamber redesigns, driving an 18-24 month replacement cycle at Samsung and other NAND leaders. The dielectric etchers market therefore benefits from memory spending even during logic lulls, buffering revenue volatility.

State-of-the-art dielectric chambers cost USD 5-8 million, and ALE clusters can top USD 12-15 million installed. Board-level approvals and extended leasing reviews delay installs 6-12 months, especially at smaller IDMs and specialty fabs. Vendors respond with modular platforms that share RF, vacuum, and wafer-handling subsystems to spread expenses across process nodes, yet budget ceilings still trim the near-term dielectric etchers market expansion rate by 70 basis points.

Other drivers and restraints analyzed in the detailed report include:

For complete list of drivers and restraints, kindly check the Table Of Contents.

Silicon dioxide retained 38.10% dielectric etchers market share in 2025, anchoring mature logic and DRAM flows where cost trumps performance. The dielectric etchers market size for low-k materials is projected to balloon alongside a 468.12% CAGR, reflecting AI accelerators' need for minimal capacitance substrates.

Low-k adoption compels plasma chemistries that avoid carbon depletion and copper corrosion, spurring multi-frequency RF innovations that established vendors alone can commercialize at scale. Simultaneously, silicon nitride and emerging glass dielectrics hold niche roles for barrier and panel-level packaging, demanding etch selectivity previously unseen. This broadening palette obliges toolmakers to bundle in situ endpoint metrology and multi-pressure chambers, reinforcing switching costs and sustaining revenue diversity across the dielectric etchers market.

Reactive-ion etching commanded 42.26% of the dielectric etchers market in 2025 and remains the workhorse for cost-sensitive layers. However, ALE's 5.02% annual growth underscores its inevitability for GAA, 3D NAND and quantum circuits.

Manufacturers weigh throughput penalties against yield gains; pilot data show defect-density cuts of 35-45% when ALE replaces multi-step RIE on fin sidewalls. Tokyo Electron's cryogenic RIE hybrid blurs boundaries, letting fabs phase-in ALE tactically while protecting cycle-time budgets. Such hybridization keeps the dielectric etchers market fragmented, enabling mid-tier suppliers to carve out niches in microwave plasma or UV-assisted processes.

The Global Dielectric Etchers Market Report is Segmented by Dielectric Material (Silicon Dioxide, Silicon Nitride, and More), Technology (Reactive-Ion Etching, Inductively-Coupled Plasma, and More), Wafer Size (less Than 150mm, 200mm, 300mm, and More), End User (Pure-Play Foundries, Idms, MEMS and Sensor Fabs, and R&D and Pilot Lines), and Geography. The Market Forecasts are Provided in Terms of Value (USD).

Asia Pacific accounted for 64.51% of dielectric etchers market size in 2025 on the strength of Korean memory and Taiwanese logic clusters. China alone delivered 42% of Lam Research's revenue, yet export-control headwinds compel dual-sourcing and localized toolmaking. Governments across Japan, India and Singapore fund backend ecosystems, widening regional tool demand beyond legacy hubs.

North America's CHIPS Act disperses over USD 33 billion across 21 states, underwriting four green-field mega-fabs that each require more than 500 dielectric chambers. Domestic sourcing clauses open share for suppliers with U.S. assembly lines, nudging global allocation away from single-region dependence.

Europe pursues sovereignty via the EU Chips Act, with Germany and France courting memory and analog giants. Though the continent's aggregate share trails Asia, growth rates accelerate as sovereign procurement pushes comprehensive tool suites rather than add-ons. These shifts collectively steady the dielectric etchers market by diversifying geographic revenue streams against regional policy shocks.